## K1603TE Series 14 pin DIP, 5.0 Volt, CMOS/TTL, VCXO

- Former Champion Product

- Clocking "Sync" to NTSC Video Standards, Reference Signal, Signal Tracking

- Stratum 3 Compliant

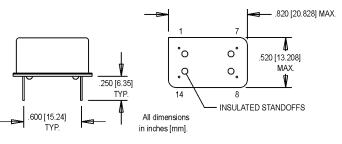

## **Pin Connections**

| PIN | FUNCTION        |  |  |  |  |

|-----|-----------------|--|--|--|--|

| 1   | Tristate        |  |  |  |  |

| 7   | Ground/Case Gnd |  |  |  |  |

| 8   | Output          |  |  |  |  |

| 14  | +Vdd            |  |  |  |  |

|    | <u> </u>              |  |  |  |

|----|-----------------------|--|--|--|

|    | .400 [10.16]<br>MAX.  |  |  |  |

| TT | <u> </u>              |  |  |  |

|    | .018 [0.46] DIA. TYP. |  |  |  |

|    | 300 [7.62] TYP.       |  |  |  |

|                           | PARAMETER             | Symbol | Min.                                       | Тур.                 | Max.   | Units   | Condition/Notes     |

|---------------------------|-----------------------|--------|--------------------------------------------|----------------------|--------|---------|---------------------|

|                           | Frequency Range       | F      | 2                                          |                      | 30     | MHz     |                     |

|                           | Operating Temperature | TA     | -40                                        |                      | +85    | °C      |                     |

|                           | Storage Temperature   | Ts     | -40                                        |                      | +85    | °C      |                     |

|                           | Frequency Stability   | ∆F/F   |                                            |                      | ±4.6   | ppm     |                     |

|                           | Aging (10 Year)       |        | -2                                         |                      | +2     | ppm     |                     |

| Suc                       | Input Voltage         | Vdd    | 4.75                                       | 5.0                  | 5.25   | ٧       |                     |

| atic                      | Input Current         | ldd    |                                            |                      | 20     | mA      |                     |

| ≝                         | Output Type           |        |                                            |                      |        |         | HCMOS/TTL           |

| ĕ                         | Load                  |        | 5 TTL or 15                                | 5 TTL or 15 pF HCMOS |        |         | See Note 1          |

| \ <u>\frac{\pi}{2}</u>    | Symmetry (Duty Cycle) |        |                                            |                      |        |         | See Note 2          |

| Electrical Specifications | <14 MHz               |        | 45                                         |                      | 55     | %       |                     |

| le Cl                     | ≥14 MHz               |        | 40                                         |                      | 60     | %       |                     |

| ш                         | Logic "1" Level       | Voh    | 4.5                                        |                      |        | ٧       |                     |

|                           | Logic "0" Level       | Vol    |                                            |                      | 0.5    | ٧       |                     |

|                           | Rise Time             | Tr     |                                            | 3.5                  | 9.0    | ns      |                     |

|                           | Fall Time             | Tf     |                                            | 2.0                  | 8.0    | ns      |                     |

|                           | Tristate Function     |        | Input Logic "1" or N/C: output active      |                      |        |         |                     |

|                           |                       |        | Input Logic "0": output disables to high-Z |                      |        |         |                     |

|                           | Start up Time         |        |                                            |                      | 10     | ms      |                     |

|                           | Phase Noise (Typical) | 10 Hz  | 100 Hz                                     | 1 kHz                | 10 kHz | 100 kHz | Offset from carrier |

|                           | @ 20 MHz              | -80    | -108                                       | -125                 | -132   | -155    | dBc/Hz              |

- 1. TTL load see load circuit diagram #1. HCMOS load see load circuit diagram #2.

- 2. Symmetry is measured at 1.4 V with TTL load, and at 50% Vdd with HCMOS load.

MtronPTI reserves the right to make changes to the product(s) and service(s) described herein without notice. No liability is assumed as a result of their use or application.

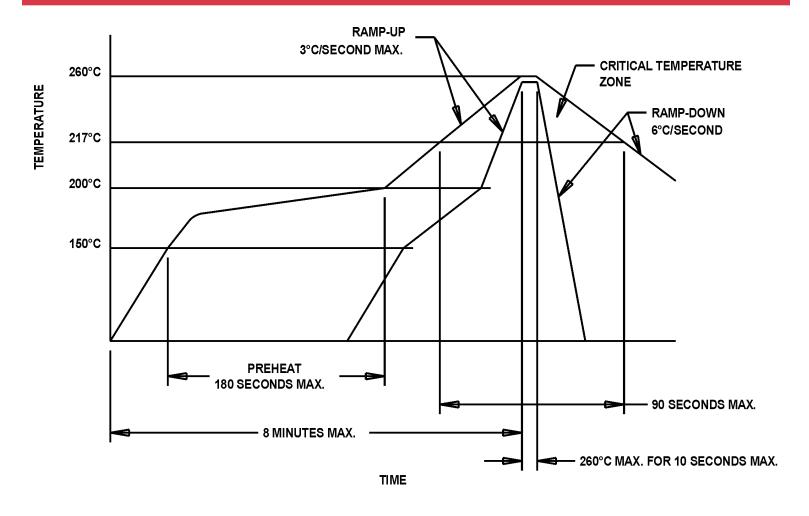

## MtronPTI Lead Free Solder Profile